| 问题 | 芯片栅极堆叠 | 芯片栅极宽度 |

|---|---|---|

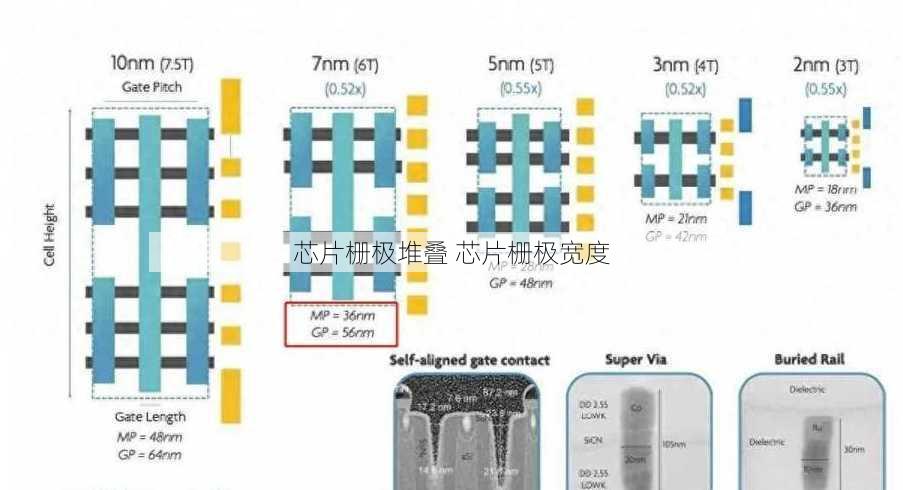

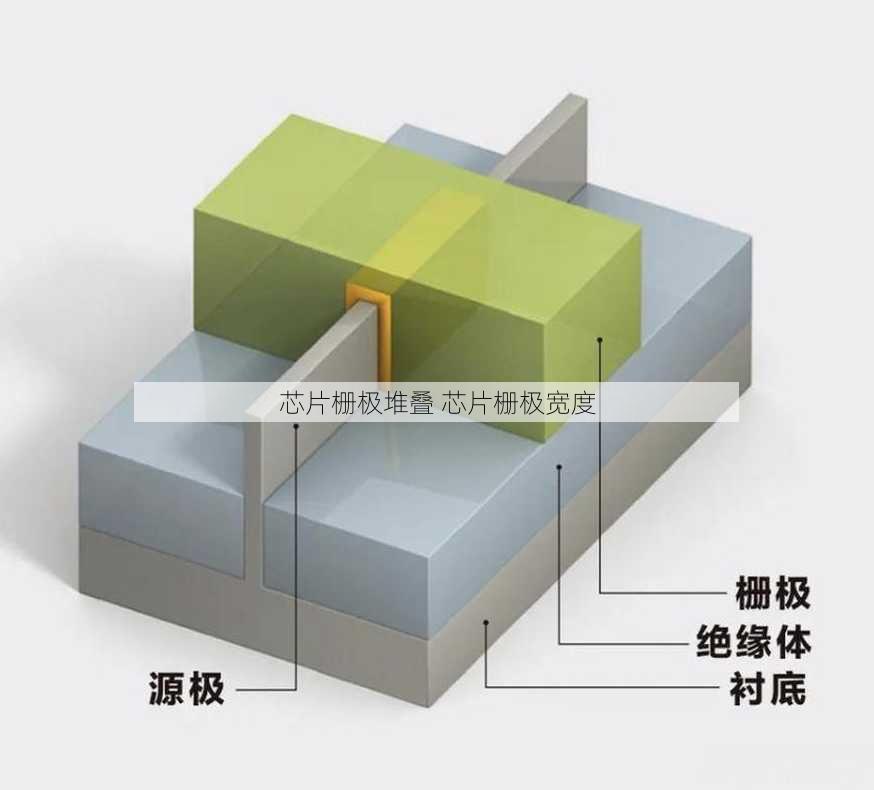

| 定义 | 芯片栅极堆叠是指在集成电路中,将多个栅极层堆叠在一起,以实现更高的晶体管密度和更优的性能。这种设计可以减少芯片的面积,提高电路的集成度。 | 芯片栅极宽度是指单个栅极的宽度,它是衡量晶体管尺寸和性能的重要参数。栅极宽度越小,晶体管的开关速度越快,功耗越低,但制造难度也相应增加。 |

| 技术优势 | 1. 提高晶体管密度:通过堆叠栅极,可以在相同面积内放置更多的晶体管,从而提高芯片的集成度。 |

2. 改善性能:堆叠栅极可以减少晶体管之间的距离,降低信号延迟,提高电路的运行速度。

降低功耗:通过优化栅极堆叠结构,可以降低晶体管的静态功耗和动态功耗。 | 1. 提高开关速度:较小的栅极宽度可以减少晶体管的延迟,从而提高电路的运行速度。

降低功耗:较窄的栅极可以减少晶体管在开关过程中的能量消耗,有助于降低整个芯片的功耗。

改善热管理:较小的栅极宽度有助于提高芯片的热传导效率,从而改善热管理。 |

| 技术挑战 | 1. 制造难度:栅极堆叠技术对制造工艺要求较高,需要精确的制造设备和严格的工艺控制。 2. 设计复杂性:堆叠栅极的设计需要考虑多层之间的相互作用,增加了设计的复杂性。

耐久性问题:多层堆叠可能会增加芯片的疲劳寿命问题,需要特别关注。 | 1. 制造精度:栅极宽度的制造需要极高的精度,任何微小的误差都可能导致性能下降。

材料选择:不同材料对栅极宽度有不同的影响,需要根据具体应用选择合适的材料。

热膨胀问题:随着温度的变化,栅极宽度可能会发生变化,需要考虑热膨胀对性能的影响。 |

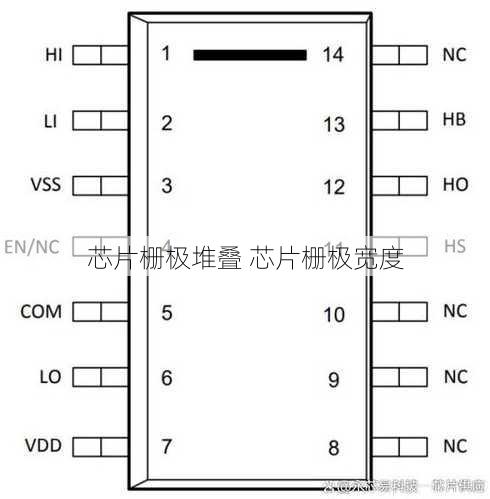

| 应用领域 | 芯片栅极堆叠技术广泛应用于高性能计算、移动设备、通信设备等领域,特别是在5G、人工智能和物联网等新兴领域。 | 芯片栅极宽度是所有集成电路设计的基础,广泛应用于各种电子设备,如计算机、手机、家电等。 |

文章版权声明:除非注明,否则均为教育生活网原创文章,转载或复制请以超链接形式并注明出处。